System Boardcon CM3576 ar y Modiwl

Manylebau

- Nodwedd: CM3576

- CPU: Cortex-A72 cwad-craidd a Cortex-A53 cwad-craidd

- RDD: 2GB LPDDR4/x (hyd at 8GB)

- eMMC: 32GB (opsiwn hyd at 128GB)

- FFLACH UFS: FLASH Power EDP/MIPI DSI I2S MIPI CSI SATA HDMI allbwn DP allbwn RGB allbwn EBC Bws Flex

- Manylebau: 1-CH EDP, 1-CH MIPI DSI, 5-CH, 3-CH, 4-Lane neu 4-CH, 2-Lane + 1-CH, 4-Lane CSI (hyd at 5 CSI Cameras), 2-CH , 1-CH (opsiwn EDP), opsiwn 1-CH, 1-CH, 24bit, 1-CH (opsiwn)

- GALL: 2-CH

- USB: 1-CH Math-C a 1-CH USB Host3.0

- Ethernet: 1-ch 1GB PHY

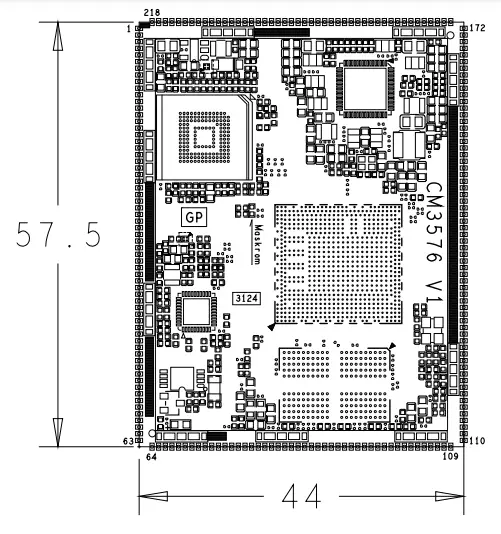

- Dimensiwn Bwrdd: 57.5 x 44mm

Cyfarwyddiadau Defnydd Cynnyrch

Gweithdrefnau Gosod

- Cysylltwch y mewnbwn pŵer angenrheidiol yn ôl y Diffiniadau Pin.

- Sicrhau bod y system cyftagMae e o fewn yr ystod benodedig (3.4V-5.5V).

- Os ydych chi'n defnyddio perifferolion fel camerâu neu arddangosiadau, cysylltwch nhw â'r porthladdoedd priodol ar y bwrdd.

Gwybodaeth Diogelwch

Defnyddiwch y mewnbwn pŵer penodedig bob amser cyftage ystod i osgoi niweidio'r bwrdd neu gydrannau.

Datrys problemau

Os byddwch yn dod ar draws unrhyw broblemau yn ystod y gosodiad neu'r gweithrediad, cyfeiriwch at yr adran datrys problemau yn y llawlyfr am arweiniad.

FAQ

- C: Beth ddylwn i ei wneud os nad yw'r bwrdd yn pŵer ymlaen?

A: Gwiriwch y cysylltiadau pŵer a sicrhewch y cyftage o fewn yr ystod benodedig. Os bydd y mater yn parhau, cyfeiriwch at yr adran datrys problemau yn y llawlyfr. - C: A allaf uwchraddio'r gallu DDR?

A: Oes, gellir uwchraddio'r gallu DDR hyd at 8GB yn unol â'r manylebau a grybwyllir.

CM3576 Llawlyfr Defnyddiwr Cyfeirio

v1.20240628

Dyluniad Embedded Boardcon

www.armdesigner.com

Rhagymadrodd

Am y Llawlyfr hwn

Bwriad y llawlyfr hwn yw rhoi trosodd i'r defnyddiwrview o'r bwrdd a buddion, cwblhau manylebau nodweddion, a sefydlu gweithdrefnau. Mae'n cynnwys gwybodaeth ddiogelwch bwysig hefyd.

Adborth a Diweddariad i'r Llawlyfr hwn

Er mwyn helpu ein cwsmeriaid i wneud y gorau o'n cynnyrch, rydym yn barhaus yn sicrhau bod adnoddau ychwanegol a diweddar ar gael ar y Boardcon websafle (www.boardcon.com, www.armdesigner.com).

Mae'r rhain yn cynnwys llawlyfrau, nodiadau cais, rhaglennu examples, a meddalwedd a chaledwedd wedi'u diweddaru. Dewch i mewn o bryd i'w gilydd i weld beth sy'n newydd!

Pan fyddwn yn blaenoriaethu gwaith ar yr adnoddau hyn sydd wedi'u diweddaru, adborth gan gwsmeriaid yw'r dylanwad mwyaf, Os oes gennych gwestiynau, sylwadau neu bryderon am eich cynnyrch neu brosiect, peidiwch ag oedi cyn cysylltu â ni yn cefnogaeth@armdesigner.com.

Gwarant Cyfyngedig

Mae Boardcon yn gwarantu bod y cynnyrch hwn yn rhydd o ddiffygion mewn deunydd a chrefftwaith am gyfnod o flwyddyn o'r dyddiad prynu. Yn ystod y cyfnod gwarant hwn bydd Boardcon yn atgyweirio neu'n disodli'r uned ddiffygiol yn unol â'r broses ganlynol:

Rhaid cynnwys copi o'r anfoneb wreiddiol wrth ddychwelyd yr uned ddiffygiol i Boardcon. Nid yw'r warant gyfyngedig hon yn cynnwys iawndal sy'n deillio o oleuadau neu ymchwyddiadau pŵer eraill, camddefnyddio, cam-drin, amodau gweithredu annormal, neu ymdrechion i newid neu addasu swyddogaeth y cynnyrch.

Mae'r warant hon yn gyfyngedig i atgyweirio neu ailosod yr uned ddiffygiol. Ni fydd Boardcon mewn unrhyw achos yn atebol nac yn gyfrifol am unrhyw golled neu iawndal, gan gynnwys ond heb fod yn gyfyngedig i unrhyw elw a gollwyd, iawndal achlysurol neu ganlyniadol, colli busnes, neu elw rhagweladwy sy'n deillio o ddefnyddio'r cynnyrch hwn neu anallu i'w ddefnyddio.

Mae atgyweiriadau a wneir ar ôl i'r cyfnod gwarant ddod i ben yn destun tâl atgyweirio a chost llongau dychwelyd. Cysylltwch â Boardcon i drefnu unrhyw wasanaeth atgyweirio ac i gael gwybodaeth am daliadau atgyweirio.

CM3576 Cyflwyniad

Crynodeb

Mae system-ar-modiwl CM3576 wedi'i gyfarparu â RK356 Rockchip, mae ganddo Cortex-A72 cwad-craidd a phrosesydd Cortex-A53 cwad-craidd, Embedded Mali-G52 MC3 GPU a 6.0 TOPs NPU.

Fe'i cynlluniwyd yn benodol ar gyfer y dyfeisiau perfformiad uchel fel system gwyliadwriaeth fideo 4K, dyfeisiau cyfrifo AI Edge, dyfeisiau rhyngweithiol deallus, cyfrifiaduron personol a robotiaid. Gall yr ateb peiriant prosesu a chyflymu amlgyfrwng perfformiad uchel helpu cwsmeriaid i gyflwyno technolegau newydd yn gyflymach a gwella effeithlonrwydd datrysiad cyffredinol.

Nodweddion

- Microbrosesydd

- Cortex-A72 Quad-core hyd at 2.2GHz

- Cortex-A53 Quad-core hyd at 1.8GHz

- 48KB I-cache 32KB D-cache a 1MB L2 ar gyfer A72 pob craidd, 32KB I-cache 32KB D-cache a 512KB L2 ar gyfer A53 pob craidd

- 6.0 TOPS Uned Prosesau Niwral

- Mali-G52 MC3 hyd at 1.0GHz

- Cwad-craidd Cortex-M0 ar gyfer cais defnyddiwr

- Sefydliad Cof

- LPDDR4 neu LPDDR4X RAM hyd at 16GB

- EMMC hyd at 128GB

- Cefnogwch UFS hyd at 128GB

- Cefnogi FSPI Flash

- Boot ROM

- Yn cefnogi lawrlwytho cod system trwy USB OTG

- System ddiogel

- Mewnosod dwy injan seiffr

- Cefnogi ysgol allweddol i warantu allwedd yn ddiogel

- Cefnogi OS diogel a sgramblo data

- Cefnogi OTP

- Datgodiwr Fideo / Amgodiwr

- Yn cefnogi datgodio fideo hyd at 8K@30fps

- Yn cefnogi amgodio H.265 hyd at 8K@30fps neu 4K@120fps

- H.264 HP amgodio hyd at 4K@60fps

- Maint llun hyd at 65520 x 65520

- Is-System Arddangos

- Allbwn Fideo

- Yn cefnogi HDMI 2.1 TX gydag ARC, hyd at 4K@120fps Neu ryngwyneb EDP TX hyd at 4K@60Hz

- Mae HDMI 2.1 yn cefnogi modd FRL

- Yn cefnogi 4 lôn MIPI DSI hyd at 4K@60Hz

- Yn cefnogi rhyngwyneb PD1.4a hyd at 4K@60fps

- Yn cefnogi allbwn RGB 24bit

- Yn cefnogi rhyngwyneb sgrin E-inc

- Mewnbwn Fideo/Delwedd

- Yn cefnogi rhyngwynebau CSI 3-CH MIPI 4lanes neu ryngwynebau CSI 4-CH MIPI 2lanes + 1-CH 4lanes

- Yn cefnogi mewnbwn DVP 8-bit

- Sain

- Pum rhyngwyneb I2S/PCM

- Cefnogi 8-ch TX/RX ar I2S0/1

- Cefnogi arae Mic Hyd at 8ch PDM/TDM rhyngwyneb

- Cefnogi allbwn SPDIF 2-ch

- Cefnogi mewnbwn SPDIF 2-ch

- Cefnogi canfod gweithgaredd llais

- USB / PCIE/SATA3

- Dau ryngwyneb USB2.0 OTG

- Un rhyngwyneb Math-C neu DP

- Un Gwesteiwr USB3.0 neu ryngwyneb PCIE2.1 × 1 neu SATA3.

- Un rhyngwyneb PCIE2.1 × 1 neu SATA3.

- Mae SATA3 yn cefnogi pum dyfais bob porthladd trwy switsh PM

- Ethernet

- Ar fwrdd RTL8211F/ YT8531

- I2C

- Hyd at 9-CH I2C

- Cefnogi modd safonol a modd cyflym (hyd at 400kbit yr eiliad)

- I3C

- Hyd at 2-CH I3C

- Cefnogi modd HDR (hyd at 30Mbps)

- I2C gydnaws

- SDIO / SDMMC

- Cefnogi protocol SDIO 3.0

- Cefnogi cerdyn SD3.0

- SPI

- Hyd at reolwyr SPI 5-ch,

- Rhyngwyneb cyfresol cydamserol deublyg llawn

- UART

- Cefnogi hyd at 12 UARTs

- UART2 gyda 2 wifren ar gyfer dadfygio

- Gwreiddio dau FIFO 64byte

- CAN

- Cefnogi hyd at ddau reolwr CAN

- Cefnogi protocol CAN FD

- ADC

- Hyd at ddwy sianel ADC

- Cydraniad 12-did hyd at 1MS/ssampcyfradd ling

- Cyftage ystod mewnbwn rhwng 0V i 1.8V

- PWM

- Hyd at 4 PWM gyda gweithrediad yn seiliedig ar ymyrraeth

- Cefnogi cyfleuster amser/cownter 32bit

- Uned bŵer

- PMU RK806 ar fwrdd

- 3.4 ~ 5.5V prif fewnbwn pŵer

- Allbwn 1.8V a 3.3V ar y mwyaf 500mA

- RTC isel iawn yn defnyddio cerrynt, llai 5uA ar Gell botwm 3V.

Diagram Bloc CM3576

Diagram Bloc RK3576

Bwrdd datblygu (EM3576) Diagram Bloc

CM3576 manylebau

| Nodwedd | Manylebau |

| CPU | Cortex-A72 cwad-craidd a Cortex-A53 cwad-craidd |

| DDR | 2GB LPDDR4/x (hyd at 8GB) |

| eMMC FFLACH | 32GB (hyd at 128GB) |

| FFLACH UFS | opsiwn |

| Grym | DC 3.4 ~ 5.5V |

| EDP/MIPI DSI | 1-CH EDP, 1-CH MIPI DSI |

| I2S | 5-CH |

| MIPI CSI | 3-CH 4-Lane neu 4-CH 2-Lane + 1-CH 4-Lan CSI (hyd at 5 Camera CSI) |

| SATA | 2-CH |

| allbwn HDMI | 1-CH (opsiwn EDP) |

| Allbwn DP | 1-CH |

| Allbwn RGB | 1-CH 24bit |

| Allbwn EBC | 1-CH (opsiwn) |

| Bws Flex | opsiwn |

| Nodwedd | Manylebau |

| CAN | 2-CH |

| USB | 1-CH Math-C a 1-CH USB Host3.0 |

| Ethernet | 1-ch 1GB PHY |

| SDMMC | 2-CH |

| SPDIF TX | 2-CH |

| SPDIF RX | 2-CH |

| I2C | 9-CH |

| I3C | 2-CH |

| SPI | 5-CH |

| CAN | 2-CH |

| UART | 11-CH, 1-CH(DEBUG) |

| PWM | 4-CH |

| ADC YN | 2-CH |

| Dimensiwn Bwrdd | 57.5 x 44mm |

Dimensiwn PCB CM3576

Diffiniad Pin CM3576

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

| 1 | VCC_SYS | Mewnbwn Pwer System | 3.4V-5.5V | |

| 2 | VCC_SYS | Mewnbwn Pwer System | 3.4V-5.5V | |

| 3 | VCC_SYS | Mewnbwn Pwer System | 3.4V-5.5V | |

| 4 | PWRON_L | Mewnbwn Allwedd Pwer | 3.4V-5.5V | |

| 5 | VCC_3V3_S3 | Allbwn pŵer GPIO 3.3V | Uchafswm 500mA | 3.3V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

| 6 | UART0_TX_M0 | Ar gyfer rhagosodiad dadfygio | GPIO0_D4_u | 3.3V |

| 7 | UART0_RX_M0 | Ar gyfer rhagosodiad dadfygio | GPIO0_D5_u | 3.3V |

| 8 | GND | Daear | 0V | |

| 9 | RESET_L | GPIO0_A1_z wedi'i gysylltu(PU) | 1.8V | |

| 10 | SDMMC0_DET_L_1V8 | (PU100K) | GPIO0_A7_u | 1.8V |

|

11 |

WIFI_WAKE_HOST_H

_1V8 |

I2C0_SCL_M0 |

GPIO0_B0_z |

1.8V |

|

12 |

BT_WAKE_HOST_H_1

V8 |

I2C0_SDA_M0 |

GPIO0_B1_z |

1.8V |

|

13 |

HOST_WAKE_BT_H_1 V8 |

SPDIF_TX1_M2/SPI2_CLK_ M1/PDM0_CLK1_M2/CLK1_

32K_OUT/SATA_MPSWIT |

GPIO1_D5_ch |

1.8V |

|

14 |

SAI2_SCLK_M0_1V8 |

I3C0_SDA_PU_M1/UART10

_RX_M1 |

GPIO1_D1_ch |

1.8V |

| 15 | SAI2_SDO_M0_1V8 | UART10_TX_M1 | GPIO1_D0_ch | 1.8V |

|

16 |

SAI2_SDI_M0_1V8 |

I3C0_SDA_M1/PWM1_CH4_

M1 |

GPIO1_D3_ch |

1.8V |

|

17 |

SAI2_LRCK_M0_1V8 |

I3C0_SCL_M1/PWM1_CH3_

M1 |

GPIO1_D2_ch |

1.8V |

|

18 |

WIFI_REG_ON_H_1V8 |

I2C8_SCL_M1/UART2_TX_ M0/PDM0_SDI0_M2/SATA_

CPPOD |

GPIO1_C6_d |

1.8V |

|

19 |

BT_REG_ON_H_1V8 |

I2C8_SDA_M1/UART2_RX_

M0/PDM0_SDI1_M2/SATA_ CPDET |

GPIO1_C7_d |

1.8V |

|

20 |

UART4_CTSN_M1_1V

8 |

SDMMC1_DET_M0/I2C6_S

DA_M1/SPI2_CSN0_M1 |

GPIO1_C3_u |

1.8V |

|

21 |

UART4_RTSN_M1_1V 8 |

SDMMC1_PWEN_M0/I2C6_ SCL_M1/SPI2_CSN1_M1/P

WM1_CH2_M1 |

GPIO1_C2_u |

1.8V |

|

22 |

UART4_TX_M1_1V8 |

SPI2_MOSI_M1/UART2_RT

S_M0/PCIE0_BUTTONRST |

GPIO1_C4_d |

1.8V |

| 23 | UART4_RX_M1_1V8 | SPI2_MISO_M1/UART2_CT

S_M0/PCIE1_BUTTONRST |

GPIO1_C5_d | 1.8V |

| 24 | SDMMC1_D1_M0_1V8 | I2C9_SCL_M1/SPI1_MOSI_

M0/PCIE1_WAKE_M1/SAI3_ LRCK_M1/PWM1_CH1_M1 |

GPIO1_B5_ch | 1.8V |

| 25 | SDMMC1_D0_M0_1V8 | I2C9_SDA_M1/SPI1_CLK_M 0/PCIE1_CLKREQ_M1/SAI3

_SCLK_M1/PWM1_CH0_M1 |

GPIO1_B4_ch | 1.8V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

|

26 |

SDMMC1_D2_M0_1V8 |

UART3_CTS_M2/SPI1_MIS O_M0/PCIE0_CLKREQ_M1/

SAI3_SDO_M1 |

GPIO1_B6_ch |

1.8V |

|

27 |

SDMMC1_D3_M0_1V8 |

UART3_RTS_M2/SPI1_CSN 0_M0/PCIE0_WAKE_M1/SAI

3_SDI_M1 |

GPIO1_B7_ch |

1.8V |

|

28 |

SDMMC1_CMD_M0_1 V8 |

UART3_TX_M2/SPI1_CSN1

_M0/PDM0_SDI2_M2/PWM0 _CH0_M1 |

GPIO1_C0_d |

1.8V |

|

29 |

SDMMC1_CLK_M0_1V

8 |

UART3_RX_M2/PDM0_CLK

0_M2/SAI3_MCLK_M1 |

GPIO1_C1_d |

1.8V |

| 30 | GND | Daear | 0V | |

|

31 |

RECOVERY_SRADC

_VIN1 |

ADFERIAD

MODE/ADC_IN1(PU10K) |

1.8V |

|

| 32 | SARADC_VIN2 | ADC_IN2 | 1.8V | |

| 33 | GND | Daear | 0V | |

|

34 |

SDMMC0_CLK |

I3C1_SDA_PU_M1/I2C5_SC

L_M0/UART5_TX_M2/SPI0_ CLK_M1/SAI3_SCLK_M3 |

GPIO2_A5_d/ FSPI1_CLK_M0 |

3.3V |

|

35 |

SDMMC0_D1 |

DSM_ALN_M0/I2C8_SDA_M 0/UART0_TX_M1/UART7_T X_M2/SPI0_MISO_M1/CAN0

_TX_M0/SAI3_MCLK_M3 |

GPIO2_A1_d/ PWM2_CH3_M0/ FSPI1_D1_M0 |

3.3V |

|

36 |

SDMMC0_D0 |

DSM_ALP_M0/I2C8_SCL_M 0/UART0_RX_M1/UART7_R X_M2/SPI0_MOSI_M1/CAN0

_RX_M0 |

GPIO2_A0_d/ PWM2_CH2_M0/ FSPI1_D0_M0 |

3.3V |

|

37 |

SDMMC0_CMD |

I2C5_SDA_M0/UART5_RX_ M2/SPI0_CSN0_M1/SAI3_S

DO_M3 |

GPIO2_A4_d/ PWM2_CH4_M0/

FSPI1_CSN0_M0 |

3.3V |

|

38 |

SDMMC0_D3 |

I3C1_SDA_M1/DSM_ARN_ M0/UART5_CTSN_M2/SAI3

_SDI_M3/CAN1_TX_M0 |

GPIO2_A3_d/

FSPI1_D3_M0/ JTAG_TMS_M0 |

3.3V |

|

39 |

SDMMC0_D2 |

I3C1_SCL_M1/DSM_ARP_M

0/UART5_RTSN_M2/SAI3_L RCK_M3/CAN1_RX_M0 |

GPIO2_A2_d/

FSPI1_D2_M0/ JTAG_TCK_M0 |

3.3V |

|

40 |

LCDC_DEN/EBC_SDL E/DSMC_DATA0 |

I2C3_SCL_M2/UART5_RX_ M0/SPI3_CLK_M1/SAI1_SDI

1_M1/FLEXBUS1_D1 |

GPIO3_D4_ch |

3.3V |

|

41 |

LCDC_VSYNC/EBC_S DCLK/DSMC_CLKN |

UART5_CTS_M0/SPI3_MOS

I_M1/SAI1_SDI3_M1/FLEXB US1_CLK/PWM2_CH6_M3 |

GPIO3_D6_ch |

3.3V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

|

42 |

LCDC_HSYNC/EBC_G DCLK/DSMC_CLKP |

I2C3_SDA_M2/UART5_TX_ M0/SPI3_MISO_M1/SAI1_S

DI2_M1/FLEXBUS1_D0 |

GPIO3_D5_ch |

3.3V |

|

43 |

LCDC_CLK/EBC_SDO E/DSMC_RESETN |

UART5_RTS_M0/SPI3_CSN 1_M1/SAI4_SCLK_M1/FLEX BUS1_D12_M0/FLEXBUS0_ D15_M0/FLEXBUS1_CSn_M

1/CAM_CLK0_OUT_M0 |

GPIO3_D7_d/ PWM2_CH7_M3 |

3.3V |

|

44 |

DSMC_INT0/GPIO4_A 0_d |

I2C7_SCL_M2/UART3_TX_ M0/SPI1_CSN1_M2/SAI4_L RCK_M1/FLEXBUS1_D14_ M0/FLEXBUS0_D13_M0/FL EXBUS1_CSn_M3/CAM_CL

K1_OUT_M0 |

GPIO4_A0_d/ MIPI_TE_M2/ SPDIF_RX0_M1 |

3.3V |

|

45 |

DSMC_INT2/GPIO4_A 1_d |

I2C7_SDA_M2/UART3_RX_ M0/SAI4_SDO_M1/FLEXBU S1_D13_M0/FLEXBUS0_D1 4_M0/FLEXBUS0_CSn_M1/

CAM_CLK2_OUT_M0 |

GPIO4_A1_d/ VO_POST_EMPTY/ SPDIF_TX0_M1 |

3.3V |

|

46 |

PHY1_LED1/CFG_LD

O0 |

LED cyflymder(PD4.7K) |

3.3V |

|

|

47 |

PHY1_LED2/CFG_LD

O1 |

Cyswllt LED(PD4.7K) |

3.3V |

|

| 48 | PHY1_MDI0+ | 0.5V | ||

| 49 | PHY1_MDI0- | 0.5V | ||

| 50 | PHY1_MDI1+ | 0.5V | ||

| 51 | PHY1_MDI1- | 0.5V | ||

| 52 | PHY1_MDI2+ | 0.5V | ||

| 53 | PHY1_MDI2- | 0.5V | ||

| 54 | PHY1_MDI3+ | 0.5V | ||

| 55 | PHY1_MDI3- | 0.5V | ||

| 56 | 32KOUT_RTC_1V8 | RTC_CLK 32.768KHz allbwn | GPIO0_A2_ch | 1.8V |

| 57 | VCC_RTC | Mewnbwn RTC Power | 1.8 ~ 3.3V | |

|

58 |

LCDC_D0/EBC_SDDO 0/DSMC_CSN0 |

I3C1_SCL_M2/UART2_CTS

_M2/SAI2_SDO_M2/FLEXB US1_D2 |

GPIO3_D3_d/ PWM2_CH5_M3 |

3.3V |

|

59 |

LCDC_D1/EBC_SDDO 1/DSMC_CSN3 |

I3C1_SDA_M2/UART2_RTS

_M2/SPI4_CSN1_M1/SAI2_ SDI_M2/FLEXBUS0_D12/FL EXBUS0_CS_M3/FLEXBUS 1_D15_M0 |

GPIO3_D2_d/ PWM2_CH4_M3 |

3.3V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

|

60 |

LCDC_D2/EBC_SDDO 2/DSMC_CSN2 |

I3C1_SDA_PU_M2/SPI4_CL K_M1/SAI2_MCLK_M2/FLEX BUS0_D11/FLEXBUS1_CS_

M2 |

GPIO3_D1_ch |

3.3V |

|

61 |

LCDC_D3/EBC_SDDO 3/DSMC_DATA1 |

UART8_CTS_M0/SPI1_CSN 0_M2/SAI1_MCLK_M1/FLEX

BUS1_D3 |

GPIO3_D0_d/ PWM2_CH3_M3 |

3.3V |

|

62 |

LCDC_D4/EBC_SDDO 4/DSMC_DATA2 |

UART8_RTS_M0/SPI1_CLK

_M2/SAI1_SCLK_M1/FLEXB US1_D4 |

GPIO3_C7_d |

3.3V |

|

63 |

LCDC_D5/EBC_SDDO 5/DSMC_DATA3 |

UART8_TX_M0/SPI1_MOSI

_M2/SAI1_LRCK_M1/FLEXB US1_D5 |

GPIO3_C6_d |

3.3V |

|

64 |

LCDC_D6/EBC_SDDO 6/DSMC_DATA4 |

UART8_RX_M0/SPI1_MISO

_M2/SAI1_SDO0_M1/FLEXB US1_D6 |

GPIO3_C5_d/ PWM2_CH2_M3 |

3.3V |

|

65 |

LCDC_D7/EBC_SDDO 7/DSMC_DATA5 |

I2C5_SCL_M3/UART11_TX_ M0/SPI2_CSN0_M2/SAI1_S DO0_M1/FLEXBUS1_D7/CA

N0_TX_M3 |

GPIO3_C4_d |

3.3V |

|

66 |

LCDC_D8/EBC_SDDO 8/DSMC_INT3 |

I2C9_SDA_M3/UART11_CT S_M0/SPI4_MOSI_M1/SAI2_ LRCK_M2/FLEXBUS0_D10/

FLEXBUS0_CSN_M2 |

GPIO3_C3_d/ PWM2_CH1_M3 |

3.3V |

|

67 |

LCDC_D9/EBC_SDDO 9/DSMC_INT1 |

I2C9_SCL_M3/UART11_RTS

_M0/SPI4_MISO_M1/SAI2_S CLK_M2/FLEXBUS0_D9 |

GPIO3_C2_d/ PWM2_CH0_M3 |

3.3V |

|

68 |

LCDC_D10/EBC_SDD O10/DSMC_DATA6 |

I2C5_SCL_M3/UART11_RX_ M0/SPI2_MISO_M2/SAI1_S DO2_M1/FLEXBUS1_D8/CA

N0_RX_M3 |

GPIO3_C1_d |

3.3V |

|

69 |

LCDC_D11/EBC_SDD O11/DSMC_DATA7 |

I2C4_SCL_M3/UART2_TX_ M2/UART3_RTS_M1/SAI1_S

DO3_M1/FLEXBUS1_D9 |

GPIO3_C0_d |

3.3V |

|

70 |

LCDC_D12/EBC_SDD O12/DSMC_DQS0 |

I2C4_SDA_M3/UART2_RX_ M2/UART3_CTS_M1/SAI1_S DO0_M1/FLEXBUS1_D10/F

LEXBUS1_CSN_M0 |

GPIO3_B7_ch |

3.3V |

|

71 |

LCDC_D13/EBC_SDD

O13/DSMC_DQS1 |

SPI3_CSN0_M1/ETH0_TXC

LK_M0/FLEXBUS0_CLK |

GPIO3_B6_d/

PWM0_CH1_M3 |

3.3V |

|

72 |

LCDC_D14/EBC_SDD O14/DSMC_DATA8 |

UART9_CTS_M1/ETH0_TX D0_M0/SPDIF_TX1_M0/FLE

XBUS0_D0 |

GPIO3_B5_d/ PWM1_CH5_M3 |

3.3V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

|

73 |

LCDC_D15/EBC_SDD O15/DSMC_DATA9 |

UART9_RTS_M1/ETH0_TX D1_M0/SPDIF_RX1_M0/FLE

XBUS0_D1 |

GPIO3_B4_d/ PWM1_CH4_M3 |

3.3V |

|

74 |

LCDC_D16/EBC_SDC E0/DSMC_DATA10 |

I2C8_SCL_M3/UART9_TX_ M1/ETH0_TXCTL_M0/PDM1

_SDI0_M2/FLEXBUS0_D2 |

GPIO3_B3_ch |

3.3V |

|

75 |

LCDC_D17/EBC_SDC E1/DSMC_DATA11 |

I2C8_SDA_M3/UART9_RX_ M1/ETH0_RXD0_M0/PDM1_

SDI1_M2/FLEXBUS0_D3 |

GPIO3_B2_ch |

3.3V |

|

76 |

LCDC_D18/EBC_SDC E2/DSMC_DATA12 |

UART10_TX_M0/SPI4_CSN 0_M1/ETH0_RXD1_M0/PDM

1_CLK0_M2/FLEXBUS0_D4 |

GPIO3_B1_d/ PWM1_CH3_M3 |

3.3V |

|

77 |

LCDC_D19/EBC_SDC E3/DSMC_CSN1 |

UART10_RX_M0/SPI2_MOS I_M2/ETH0_MCLK_M0/SAI4

_MCLK_M1/FLEXBUS0_D8 |

GPIO3_B0_d/ PWM0_CH0_M3 |

3.3V |

|

78 |

LCDC_D20/EBC_VCO M/DSMC_DATA13 |

UART10_RTS_M0/UART1_T X_M2/ETH0_RXCTL_M0/PD

M1_CLK1_M2/FlexBUS0_D5 |

GPIO3_A7_ch |

3.3V |

|

79 |

LCDC_D21/EBC_GDO E/DSMC_DATA14 |

UART10_CTS_M0/UART1_ RX_M2/ETH0_MDC_M0/PD

M1_SDI2_M2/FlexBUS0_D6 |

GPIO3_A6_d/ PWM1_CH2_M3 |

3.3V |

|

80 |

LCDC_D22/EBC_GDS P/DSMC_DATA15 |

SPI2_CSn1_M2/UART1_RT S_M2/ETH0_MDIO_M0/PDM

1_SDI3_M2/FlexBUS0_D7 |

GPIO3_A5_d/ PWM1_CH1_M3 |

3.3V |

|

81 |

LCDC_D23/EBC_SDS HR/DSMC_RDYN |

SPI2_CLK_M2/UART1_CTS

_M2/ETH0_CLKOUT_25M_ M0/SAI4_SDI_M1/FlexBUS1 _D11/FlexBUS0_CSn_M0 |

GPIO3_A4_d/ PWM1_CH0_M3 |

3.3V |

|

82 |

TIPEC_DPTX_AUX_P

UPDCTL1 |

AUPLL_CLKIN_M2/SAI1/4_

MCLK_M0 |

GPIO4_A2_ch

/PWM2_CH5_M0 |

3.3V |

|

83 |

PCIE1_CLKREQn_M2 |

I2C2_SDA_M2/UART5_CTS

_M1/SPI4_CS1_M2/SAI1_LR CK_M0/FlexBUS1_D12_M1 |

GPIO4_A5_ch |

3.3V |

|

84 |

PCIE1_PWREN_H |

I2C2_SCL_M2/UART5_RTS

_M1/SPI3_CS0_M2/SAI1_S CLK_M0/FlexBUS1_CS_M4 |

GPIO4_A3_d/ PWM2_CH4_M1 |

3.3V |

|

85 |

HDMI_TX_ON_H |

I2C4_SDA_M1/UART6_RX_ M0/SPI3_MISO_M2/SAI4_L RCK_M0/PDM1_CLK0_M1/F

lexBUS1_D14_M1/CAN0_RX _M2 |

GPIO4_A6_ch |

3.3V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

|

86 |

TIPEC_DPTX_AUX_P UPDCTL2 |

I2C4_SCL_M1/UART6_TX_ M0/SPI3_MOSI_M2/SAI4_S CLK_M0/PDM1_SDI3_M1/Fl exBUS1_D13_M1/CAN0_TX

_M2 |

GPIO4_A4_ch |

3.3V |

|

87 |

HP_CTL_H |

SPI3_CLK_M2/SAI4_SDI_M

0/SAI1_SDO0_M0 |

GPIO4_A7_d/

PWM2_CH6_M0 |

3.3V |

|

88 |

I2C3_SCL_M0_Synhwyrydd |

PCIE0_CLKREQ_M2/IUART

2_TX_M1/SPDIF_TX0_M0/Fl exBUS0_D15_M1/CAN1_TX _M2 |

GPIO4_B5_d (PU2.2K) |

3.3V |

|

89 |

I2C3_SDA_M0_Synhwyrydd |

PCIE0_WAKE_M2/IUART2_

RX_M1/SPDIF_RX0_M0/Fle xBUS0_CSN_M4/CAN1_RX _M2 |

GPIO4_B4_d (PU2.2K) |

3.3V |

|

90 |

SPK_CTL_H |

SPI3_CS1_M2/SPI4_CS0_M 2/PDM1_SDI0_M1/SAI1_SDI

0_M0/SAI4_SDO_M0 |

GPIO4_B3_d/ PWM2_CH7_M0 |

3.3V |

|

91 |

PCIE1_PERSTn |

SPI4_MISO_M2/PDM1_SDI1

_M1/SAI1_SDI1_M0/SAI1_S DO3_M0/FlexBUS1_D15_M1 |

GPIO4_B2_d/ MIPI_TE_M0 |

3.3V |

|

92 |

IRC_BIN |

UART2_CTS_M1/UART6_C TS_M0/UART5_RX_M1/SPI4

_MOSI_M2/PDM1_SDI2_M1/ SAI1_SDI2_M0/SAI1_SDO2 _M0/FlexBUS1_D14_M1 |

GPIO4_B1_ch |

3.3V |

|

93 |

IRC_AIN |

UART2_RTS_M1/UART6_R TS_M0/UART5_TX_M1/SPI4

_CLK_M2/PDM1_CLK1_M1/ SAI1_SDI3_M0/SAI1_SDO1 _M0/FlexBUS1_D13_M1 |

GPIO4_B1_ch |

3.3V |

|

94 |

PCIE0_CLKREQn_M3 |

I2C6_SCL_M3/SPI4_MISO_ M0/SAI4_SDI_M2/VP1_SYN

C_OUT/CAN1_TX_M1 |

GPIO4_C6_d/ PWM2_CH2_M1/

SATA0_ACTLED_M1 |

3.3V |

|

95 |

PCIE0_PERSTn |

I2C6_SDA_M3/SPI4_CLK_M 0/SAI4_SCLK_M2/VP2_SYN

C_OUT/CAN1_RX_M1 |

GPIO4_C7_d/ PWM2_CH3_M1 |

3.3V |

|

96 |

PWM2_CH5_M1_FAN |

I2C3_SDA_M3/UART6_RX_ M3/SPI4_MOSI_M0/SAI4_S DO_M2/VP0_SYNC_OUT/IS

P_FLASH_TRIGOUT_M1 |

GPIO4_C5_d/ PWM2_CH5_M1/ SATA1_ACTLED_M1

PCIE0_WAKE_M3 |

3.3V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

|

97 |

HDMI_TX_HPDIN_M0 |

I2C7_SDA_M3/UART11_RX

_M2/EDP_HPD_M0/PCIE1_ CLKREQ_M3/DSM_ALN_M1 |

GPIO4_C1_d/ PWM0_CH1_M1 |

3.3V |

|

98 |

HDMI_TX_SDA |

I2C2_SDA_M3/UART9_RX_

M2/CAN0_RX_M1/DSM_AR N_M1 |

GPIO4_C3_d/ PWM2_CH1_M1 |

3.3V |

|

99 |

HDMI_TX_SCL |

I2C2_SCL_M3/UART9_TX_ M2/CAN0_TX_M1/DSM_AR

P_M1 |

GPIO4_C2_d/ PWM2_CH0_M1 |

3.3V |

|

100 |

DP_HPDIN_M0 |

I2C3_SCL_M3/UART6_TX_ M3/SPI4_CSn0_M0/SAI4_LR CK_M2/ISP_PRLIGHT_TRIG

_M1 |

GPIO4_C4_d/ PWM2_CH6_M1 |

3.3V |

|

101 |

HDMI_TX_CEC_M0 |

I2C7_SCL_M3/UART11_TX_ M2/SPI4_CSn1_M0/SAI_MC

LK_M2/DSM_ALP_M1 |

GPIO4_C0_d/ PWM1_CH5_M1/

PCIE1_WAKE_M3 |

3.3V |

| 102 | GND | Daear | 0V | |

|

103 |

MIPI_DPHY_CSI0_PW REN_H_1V8 |

UART3_RTS_M0/SPI3_CSn 0_M0/SAI3_SDI_M2/ETH0_

RXD1_M1/CAN_RX_M3 |

GPIO3_A3_d/ VI_CIF_CLKI/

SPDIF_TX1_M1 |

1.8V |

|

104 |

SAI0_SDI0_M0_1V8 |

UART1_TX_M1/PDM0_SDI3

_M3/ETH0_TXD1_M1 |

GPIO2_B0_d/

VI_CIF_D13 |

1.8V |

|

105 |

SAI0_SDI1_M0_1V8 |

UART1_RX_M1/PDM0_SDI2

_M3/ETH0_TXD0_M1 |

GPIO2_B1_d/

VI_CIF_D12 |

1.8V |

|

106 |

SAI0_SDI2_M0_1V8 |

UART1_CTS_M1/SPI4_CSn 0_M3/PDM0_SDI1_M3/PCIE

0_CLKREQ_M0 |

GPIO2_B2_d/ VI_CIF_D11 |

1.8V |

|

107 |

SAI0_SDI3_M0_1V8 |

UART7_CTS_M1/SPI4_MOS I_M3/PDM0_SDI0_M3/SATA

0_ACTLED_M0 |

GPIO2_B4_d/ VI_CIF_D9 |

1.8V |

|

108 |

SAI0_SCLK_M0_1V8 |

I2C8_SCL_M2/UART8_CTS

_M1/UART7_RX_M0 |

GPIO2_B6_ch |

1.8V |

|

109 |

SAI0_LRCK_M0_1V8 |

I2C8_SDA_M2/UART8_RTS

_M1/UART7_TX_M0 |

GPIO2_B7_ch |

1.8V |

|

110 |

SAI0_MCLK_M0_1V8 |

UART7_RTS_M0/SPI4_MIS O_M3/PDM0_CLK0_M3/SAT

A1_ACTLED_M0 |

GPIO2_B5_d/ VI_CIF_D8 |

1.8V |

|

111 |

SAI0_SDO0_M0_1V8 |

I2C4_SCL_M2/UART8_TX_

M1/SPI4_CSn1_M3/ETH0_R XD0_M1 |

GPIO2_A6_d/ VI_CIF_D15 |

1.8V |

|

112 |

SAI0_SDO1_M0_1V8 |

I2C4_SDA_M2/UART8_RX_

M1/ETH0_TXCTL_M1 |

GPIO2_A7_d/

VI_CIF_D14 |

1.8V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

|

113 |

SAI0_SDO2_M0_1V8 |

UART1_RTS_M1/SPI4_CLK

_M3/PDM0_CLK1_M3/PCIE 1_CLKREQ_M0 |

GPIO2_B3_d/ VI_CIF_D10 |

1.8V |

|

114 |

SPDIF_RX1_M1_1V8 |

UART3_RTS_M0/SPI3_MIS O_M0/SAI3_SDO_M2/ETH0

_RXCTL_M1/CAN_TX_M3 |

GPIO3_A2_d/

VI_CIF_CLKO/ MIPI_TE_M1 |

1.8V |

|

115 |

I2C7_SDA_M1_1V8 |

UART3_RX_M0/SPI3_MOSI

_M0/SAI3_LRCK_M2/ETH0_ MDC_M1(PU2.2K) |

GPIO3_A1_d/ VI_CIF_VSYNC |

1.8V |

|

116 |

I2C7_SCL_M1_1V8 |

UART3_TX_M0/SPI3_CLK_

M0/SAI3_SCLK_M2/ETH0_ MDIO_M1(PU2.2K) |

GPIO3_A0_d/ VI_CIF_HREF |

1.8V |

| 117 | GND | Daear | 0V | |

| 118 | DP_TX_AUXP | 0.5V | ||

| 119 | DP_TX_AUXN | 0.5V | ||

| 120 | USB2_OTG1_DP | 0.5V | ||

| 121 | USB2_OTG1_DM | 0.5V | ||

| 122 | USB2_OTG0_DP | 0.5V | ||

| 123 | USB2_OTG0_DM | 0.5V | ||

|

124 |

USB3_OTG0_SSRX1N

/DP_TX_D0N |

0.5V |

||

|

125 |

USB3_OTG0_SSRX1P

/DP_TX_D0P |

0.5V |

||

|

126 |

USB3_OTG0_SSTX1P/

DP_TX_D1P |

0.5V |

||

|

127 |

USB3_OTG0_SSTX1N/

DP_TX_D1N |

0.5V |

||

|

128 |

USB3_OTG0_SSRX2N

/DP_TX_D2N |

0.5V |

||

|

129 |

USB3_OTG0_SSRX2P

/DP_TX_D2P |

0.5V |

||

|

130 |

USB3_OTG0_SSTX2P/

DP_TX_D3P |

0.5V |

||

|

131 |

USB3_OTG0_SSTX2N/

DP_TX_D3N |

0.5V |

||

| 132 | GND | Daear | 0V | |

|

133 |

MIPI_DPHY_DSI_TX_

D0N |

MIPI_CPHY_DSI_TX_TRIO0

A |

0.5V |

|

|

134 |

MIPI_DPHY_DSI_TX_

D0P |

MIPI_CPHY_DSI_TX_TRIO0

B |

0.5V |

|

|

135 |

MIPI_DPHY_DSI_TX_

D1N |

MIPI_CPHY_DSI_TX_TRIO0

C |

0.5V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

|

136 |

MIPI_DPHY_DSI_TX_

D1P |

MIPI_CPHY_DSI_TX_TRIO1

A |

0.5V |

|

|

137 |

MIPI_DPHY_DSI_TX_

CLKN |

MIPI_CPHY_DSI_TX_TRIO1

B |

0.5V |

|

|

138 |

MIPI_DPHY_DSI_TX_

CLKP |

MIPI_CPHY_DSI_TX_TRIO1

C |

0.5V |

|

|

139 |

MIPI_DPHY_DSI_TX_

D2N |

MIPI_CPHY_DSI_TX_TRIO2

A |

0.5V |

|

|

140 |

MIPI_DPHY_DSI_TX_

D2P |

MIPI_CPHY_DSI_TX_TRIO2

B |

0.5V |

|

|

141 |

MIPI_DPHY_DSI_TX_

D3N |

MIPI_CPHY_DSI_TX_TRIO2

C |

0.5V |

|

|

142 |

MIPI_DPHY_DSI_TX_

D3P |

0.5V |

||

|

143 |

MIPI_DPHY_CSI0_RX

_D0P |

MIPI_CPHY_CSI_TX_TRIO0

B |

0.5V |

|

|

144 |

MIPI_DPHY_CSI0_RX

_D0N |

MIPI_CPHY_CSI_TX_TRIO0

A |

0.5V |

|

|

145 |

MIPI_DPHY_CSI0_RX

_D1P |

MIPI_CPHY_CSI_TX_TRIO1

A |

0.5V |

|

|

146 |

MIPI_DPHY_CSI0_RX

_D1N |

MIPI_CPHY_CSI_TX_TRIO0

C |

0.5V |

|

|

147 |

MIPI_DPHY_CSI0_RX

_CLKP |

MIPI_CPHY_CSI_TX_TRIO1

C |

0.5V |

|

|

148 |

MIPI_DPHY_CSI0_RX

_CLKN |

MIPI_CPHY_CSI_TX_TRIO1

B |

0.5V |

|

|

149 |

MIPI_DPHY_CSI0_RX

_D2P |

MIPI_CPHY_CSI_TX_TRIO2

B |

0.5V |

|

|

150 |

MIPI_DPHY_CSI0_RX

_D2N |

MIPI_CPHY_CSI_TX_TRIO2

A |

0.5V |

|

|

151 |

MIPI_DPHY_CSI0_RX

_D3P |

0.5V |

||

|

152 |

MIPI_DPHY_CSI0_RX

_D3N |

MIPI_CPHY_CSI_TX_TRIO2

C |

0.5V |

|

| 153 | GND | Daear | 0V | |

| 154 | HDMI_TX_D3N | EDP_TX3N | 0.5V | |

| 155 | HDMI_TX_D3P | EDP_TX3P | 0.5V | |

| 156 | HDMI_TX_D0P | EDP_TX0P | 0.5V | |

| 157 | HDMI_TX_D0N | EDP_TX0N | 0.5V | |

| 158 | HDMI_TX_D1P | EDP_TX1P | 0.5V | |

| 159 | HDMI_TX_D1N | EDP_TX1N | 0.5V | |

| 160 | HDMI_TX_D2P | EDP_TX2P | 0.5V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

| 161 | HDMI_TX_D2N | EDP_TX2N | 0.5V | |

| 162 | HDMI_TX_SBDN | EDP_AUXN | 0.5V | |

| 163 | HDMI_TX_SBDP | EDP_AUXP | 0.5V | |

| 164 | GND | Daear | 0V | |

|

165 |

MIPI_DPHY_CSI2_RX

_CLKP |

0.5V |

||

|

166 |

MIPI_DPHY_CSI2_RX

_CLKN |

0.5V |

||

|

167 |

MIPI_DPHY_CSI1_RX

_CLKN |

0.5V |

||

|

168 |

MIPI_DPHY_CSI1_RX

_CLKP |

0.5V |

||

|

169 |

MIPI_DPHY_CSI1_RX

_D3N |

MIPI_DPHY_CSI2_RX_D1N |

0.5V |

|

|

170 |

MIPI_DPHY_CSI1_RX

_D3P |

MIPI_DPHY_CSI2_RX_D1P |

0.5V |

|

|

171 |

MIPI_DPHY_CSI1_RX

_D2N |

MIPI_DPHY_CSI2_RX_D0N |

0.5V |

|

|

172 |

MIPI_DPHY_CSI1_RX

_D2P |

MIPI_DPHY_CSI2_RX_D0P |

0.5V |

|

|

173 |

MIPI_DPHY_CSI1_RX

_D1N |

0.5V |

||

|

174 |

MIPI_DPHY_CSI1_RX

_D1P |

0.5V |

||

|

175 |

MIPI_DPHY_CSI1_RX

_D0N |

0.5V |

||

|

176 |

MIPI_DPHY_CSI1_RX

_D0P |

0.5V |

||

| 177 | VCC_1V8_S3 | Allbwn pŵer GPIO 1.8V | Uchafswm 500mA | 1.8V |

|

178 |

USB2_OTG1_VBUSDE

T |

Mewnbwn USB2 VBUS |

3.3V |

|

|

179 |

TP_INT_L |

I3C0_SDA_PU_M0/UART10

_RX_M2/SAI0_SDO0_M1/D P_HPD_M1 |

GPIO0_C5_d |

3.3V |

|

180 |

LCD_BL_PWM1_CH1_

M0 |

I2C1_SDA_M1/UART4_RX_

M2/REFCLK2_OUT |

GPIO0_B5_d/

PWM1_CH1_M0 |

3.3V |

|

181 |

PCIE1_WAKEn_M0 |

I2C4_SDA_M0/UART1_RTS

_M0/PDM0_SDI3_M0/SAI0_ SDO1/SDI3_M1 |

GPIO0_D3_d/ PWM2_CH0_M0 |

3.3V |

|

182 |

GPIO0_B4_ch |

I2C1_SCL_M1/UART4_TX_

M2/REFCLK1_OUT |

PWM1_CH0_M0 |

3.3V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

|

183 |

USBCC_INT_L |

SPI0_MISO_M0/PDM0_SDI1

_M0/SAI0_SDO3/SDI1_M1 |

GPIO0_D1_ch |

3.3V |

|

184 |

PCIE0_PWREN_H |

I2C3_SDA_M1/SPI0_CLK_M

0/SAI0_LRCK_M1 |

GPIO0_C7_d |

3.3V |

|

185 |

PCIE0_WAKEn_M0 |

I2C4_SCL_M0/UART1_CTS

_M0/PDM0_SDI2_M0/SAI0_ SDO2/SDI2_M1 |

GPIO0_D2_d/ PWM1_CH5_M0 |

3.3V |

|

186 |

LCD_PWREN_H |

I2C3_SCL_M1/SPI0_CSn0_

M0/SAI0_SCLK_M1 |

GPIO0_C6_d |

3.3V |

|

187 |

I2C2_SCL_M0_CC_RT

C |

UART1_TX_M0/PWM1_CH4

_M0(PU2.2K) |

GPIO0_B7_ch |

3.3V |

|

188 |

I2C2_SDA_M0_CC_RT

C |

UART1_RX_M0/PWM1_CH3

_M0(PU2.2K) |

GPIO0_C0_d |

3.3V |

|

189 |

GPIO0_C4_d |

UART10_TX_M2/PDM0_CL

K0_M0/SAI0_MCLK_M1 |

PWM0_CH0_M0 |

3.3V |

|

190 |

I2C0_SCL_M1_TP |

I3C0_SCL_M0/UART8_TX_

M2(PU2.2K) |

GPIO0_C1_d |

3.3V |

|

191 |

I2C0_SDA_M1_TP |

I3C0_SDA_M0/UART8_RX_

M2(PU2.2K) |

GPIO0_C2_d |

3.3V |

|

192 |

TP_RST_L |

SPI0_MOSI_M0/PDM0_SDI0

_M0/SAI0_SDI0_M1 |

GPIO0_D0_ch |

3.3V |

| 193 | GND | Daear | 0V | |

| 194 | PCIE0_RXP | SATA0_RXP | 0.5V | |

| 195 | PCIE0_RXN | SATA0_RXN | 0.5V | |

| 196 | PCIE0_TXN | SATA0_TXN | 0.5V | |

| 197 | PCIE0_TXP | SATA0_TXP | 0.5V | |

| 198 | PCIE0_REFCLKP | 0.5V | ||

| 199 | PCIE0_REFCLKN | 0.5V | ||

|

200 |

PCIE1_TXP |

SATA1_TXP/USB3_OTG1_S

STXP |

0.5V |

|

|

201 |

PCIE1_TXN |

SATA1_TXN/USB3_OTG1_S

STXN |

0.5V |

|

|

202 |

PCIE1_RXP |

SATA1_RXP/USB3_OTG1_S

SRXP |

0.5V |

|

|

203 |

PCIE1_RXN |

SATA1_RXN/USB3_OTG1_S

SRXN |

0.5V |

|

| 204 | PCIE1_REFCLKP | 0.5V | ||

| 205 | PCIE1_REFCLKN | 0.5V | ||

| 206 | GND | Daear | 0V | |

|

207 |

MIPI_DPHY_CSI4_RX

_CLKP |

0.5V |

| Pin | Arwydd | Disgrifiad neu swyddogaethau | cyfresol GPIO | IO Cyftage |

|

208 |

MIPI_DPHY_CSI4_RX

_CLKN |

0.5V |

||

|

209 |

MIPI_DPHY_CSI3_RX

_D3N |

MIPI_DPHY_CSI4_RX_D1N |

0.5V |

|

|

210 |

MIPI_DPHY_CSI3_RX

_D3P |

MIPI_DPHY_CSI4_RX_D1P |

0.5V |

|

|

211 |

MIPI_DPHY_CSI3_RX

_D2N |

MIPI_DPHY_CSI4_RX_D0N |

0.5V |

|

|

212 |

MIPI_DPHY_CSI3_RX

_D2P |

MIPI_DPHY_CSI4_RX_D0P |

0.5V |

|

|

213 |

MIPI_DPHY_CSI3_RX

_CLKN |

0.5V |

||

|

214 |

MIPI_DPHY_CSI3_RX

_CLKP |

0.5V |

||

|

215 |

MIPI_DPHY_CSI3_RX

_D1N |

0.5V |

||

|

216 |

MIPI_DPHY_CSI3_RX

_D1P |

0.5V |

||

|

217 |

MIPI_DPHY_CSI3_RX

_D0N |

0.5V |

||

|

218 |

MIPI_DPHY_CSI3_RX

_D0P |

0.5V |

||

Pecyn Datblygu (EM3576)

Canllaw Dylunio Caledwedd

Cyfeirnod Cylchdaith Ymylol

Pŵer Allanol

Cylchdaith Dadfygio

Cylchdaith HDMI TX

Gwrthbwyso hyd Bwrdd Mam

Gwrthbwyso hyd Bwrdd Mam

| Gwrthbwyso hyd Rhyngwyneb 0-Lane MIPI CSI4 | |||

| MIPI_CSI0_RX0_CLKP | MIPI_CSI0_RX0_D0P | (53.5) | (+40) |

| MIPI_CSI0_RX0_D1P | (35.046) | (+30) | |

| MIPI_CSI0_RX0_D2P | |||

| MIPI_CSI0_RX0_D3P | (-25.758) | (-30) | |

Bloc melyn yw gwahaniaeth hyd grŵp CM3576 CSI0.

Ôl Troed PCB

Nodweddion Trydanol Cynnyrch

Gwasgariad a Thymheredd

| Symbol | Paramedr | Minnau | Teip | Max | Uned |

|

VCC_SYS |

Systemtage |

3.4V |

4 |

5.5 |

V |

|

Isys_in |

VCC_SYS

mewnbwn Cyfredol |

1750 |

mA |

||

|

VCC_RTC |

RTC Cyftage |

1.8 |

3 |

3.4 |

V |

|

Iirtc |

Mewnbwn RTC

Cyfredol |

5 |

8 |

uA |

|

|

I3v3_allan |

VCC_3V3

allbwn Cyfredol |

500 |

mA |

||

|

I1v8_allan |

VCC_1V8

allbwn Cyfredol |

500 |

mA |

||

|

Ta |

Tymheredd Gweithredu |

0 |

70 |

°C |

|

|

Tstg |

Tymheredd Storio |

-40 |

85 |

°C |

Dibynadwyedd y Prawf

| Prawf Gweithredu Tymheredd Uchel | ||

| Cynnwys | Gweithredu 8h mewn tymheredd uchel | 55°C±2°C |

| Canlyniad | TBD | |

| Prawf Bywyd Gweithredu | ||

| Cynnwys | Gweithredu yn yr ystafell | 120awr |

| Canlyniad | TBD | |

Dogfennau / Adnoddau

|

System Boardcon CM3576 ar y Modiwl [pdfLlawlyfr Defnyddiwr CM3576 System ar Modiwl, CM3576, System ar Fodiwl, Modiwl |