Atmel ATmega2564 8bit AVR Microcontroller

Nodweddion

- Cymorth rhwydwaith gan Hidlo Cyfeiriadau PAN Lluosog â chymorth caledwedd

- Defnydd Pŵer Lleihaol â Chymorth Caledwedd Uwch

- Microreolydd 8-Did AVR® Perfformiad Uchel, Pŵer Isel

- Pensaernïaeth RISC Uwch

- 135 Cyfarwyddiadau Pwerus - Y rhan fwyaf o Gyflawni Beiciau Cloc Sengl

- Cofrestri Gweithio Diben Cyffredinol 32×8 / Lluosydd 2-gylchred Ar-Sglodyn

- Trwybwn hyd at 16 MIPS ar 16 MHz ac 1.8V – Gweithrediad Llawn Statig

- Atgofion Rhaglen a Data Anweddol

- 256K/128K/64K Beit o Fflach Hunan-Raglenadwy Mewn-System

- Dygnwch: 10'000 o Gylchoedd Ysgrifennu/Dileu @ 125°C (25'000 o Gylchoedd @ 85°C)

- EEPROM 8K/4K/2K Beit

- Dygnwch: 20'000 o Gylchoedd Ysgrifennu/Dileu @ 125°C (100'000 o Gylchoedd @ 25°C)

- SRAM Mewnol 32K/16K/8K Beit

- JTAG (Cydymffurfio â safon IEEE 1149.1) Rhyngwyneb

- Galluoedd sganio ffiniau Yn ôl y JTAG Safonol

- Cefnogaeth Dadfygio Ar-sglodion helaeth

- Rhaglennu EEPROM Fflach, Ffiwsiau a Bits Cloi drwy'r JTAG rhyngwyneb

- Nodweddion Ymylol

- Sianeli Amserydd/Cownter a PWM lluosog

- Cownter Amser Real gydag Osgilydd Ar Wahân

- Trosydd A/D 10-bit, 330 ks/s; Cymharydd Analog; Synhwyrydd Tymheredd Ar-sglodion

- Rhyngwyneb Cyfresol SPI Meistr/Caethwas

- Dau USART Cyfresol Rhaglenadwy

- Rhyngwyneb Cyfresol 2-wifren sy'n Canolbwyntio ar Beitiau

- Triniwr Ymyriadau Uwch a Moddau Arbed Pŵer

- Amserydd Watchdog gydag Osgilydd Ar-Sglodyn Ar Wahân

- Ailosod Pŵer-ymlaen a Synhwyrydd Brown-Allbwn Cerrynt Isel

- Trawsyrrydd Pŵer Isel wedi'i integreiddio'n llawn ar gyfer Band ISM 2.4 GHz

- Pwer Uchel Ampcefnogaeth lifer gan ataliad llabed ochr sbectrwm TX

- Cyfraddau Data a Gefnogir: 250 kb/s a 500 kb/s, 1 Mb/s, 2 Mb/s

- Sensitifrwydd RX -100 dBm; Pŵer Allbwn TX hyd at 3.5 dBm

- MAC â Chymorth Caledwedd (Cydnabod yn Awtomatig, Ail-Geisio'n Awtomatig)

- Cyfrifydd Symbolau IEEE 802.15.4 32 Bit

- Canfod SFD, Lledaenu; Dad-Ledaenu; Fframio; Cyfrifiadura CRC-16

- Amrywiaeth Antena a rheolaeth TX/RX / Byffer Ffrâm TX/RX 128 Beit

- Syntheseisydd PLL gyda bylchau sianel 5 MHz a 500 kHz ar gyfer Band ISM 2.4 GHz

- Diogelwch Caledwedd (AES, Generadur Ar Hap Gwir)

- Osgilyddion Grisial Integredig (32.768 kHz a 16 MHz, angen grisial allanol)

- I/O a Phecyn

- 33 Llinell I/O Rhaglenadwy

- QFN 48-pad (RoHS/Gwyrdd Llawn)

- Ystod Tymheredd: -40°C i 125°C Diwydiannol

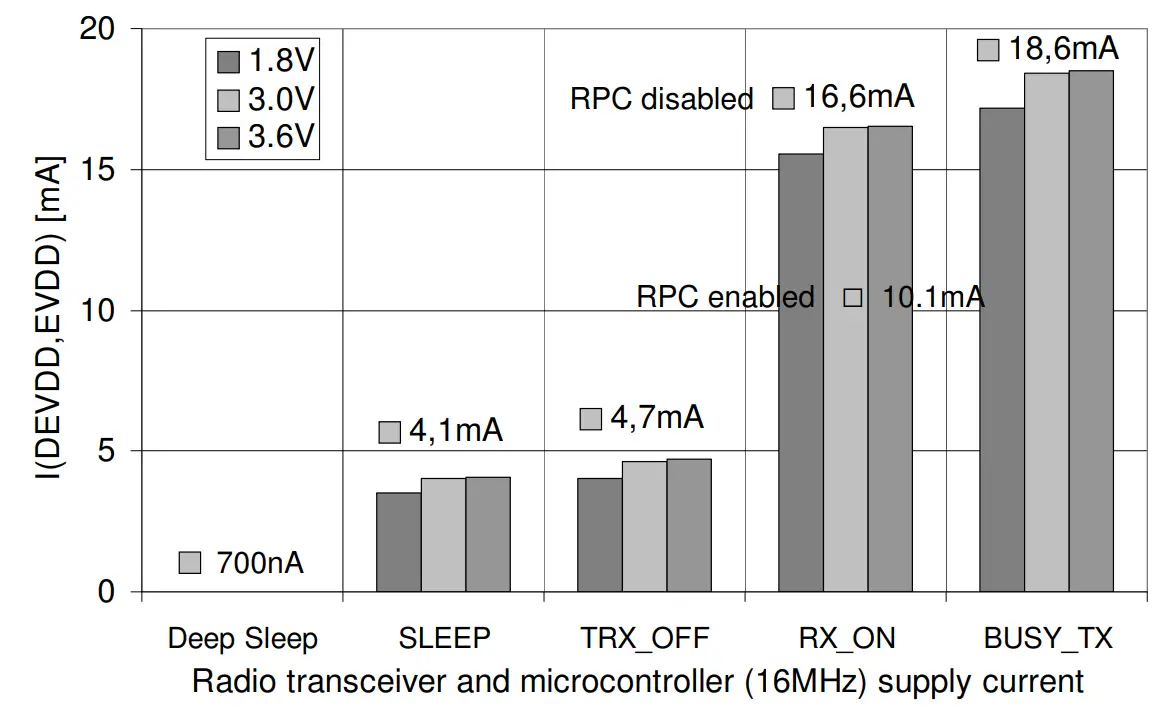

- Defnydd Pŵer Ultra Isel (1.8 i 3.6V) ar gyfer AVR a Rx/Tx: 10.1mA/18.6 mA

- Modd Gweithredol CPU (16MHz): 4.1 mA

- Trawsdderbynydd 2.4GHz: RX_ON 6.0 mA / TX 14.5 mA (pŵer allbwn TX mwyaf)

- Modd Cysgu Dwfn: <700nA @ 25°C

- Gradd Cyflymder: 0 – 16 MHz @ ystod 1.8 – 3.6V gyda chyfaint integredigtage rheoleiddwyr

Ceisiadau

- ZigBee®/ IEEE 802.15.4-2011/2006/2003™ – Dyfais Swyddogaeth Llawn a Swyddogaeth Lleihaedig

- Trawsyrrydd Band ISM 2.4GHz Diben Cyffredinol gyda Microreolydd

- RF4CE, SP100, WirelessHART™, Cymwysiadau ISM ac IPv6 / 6LoWPAN

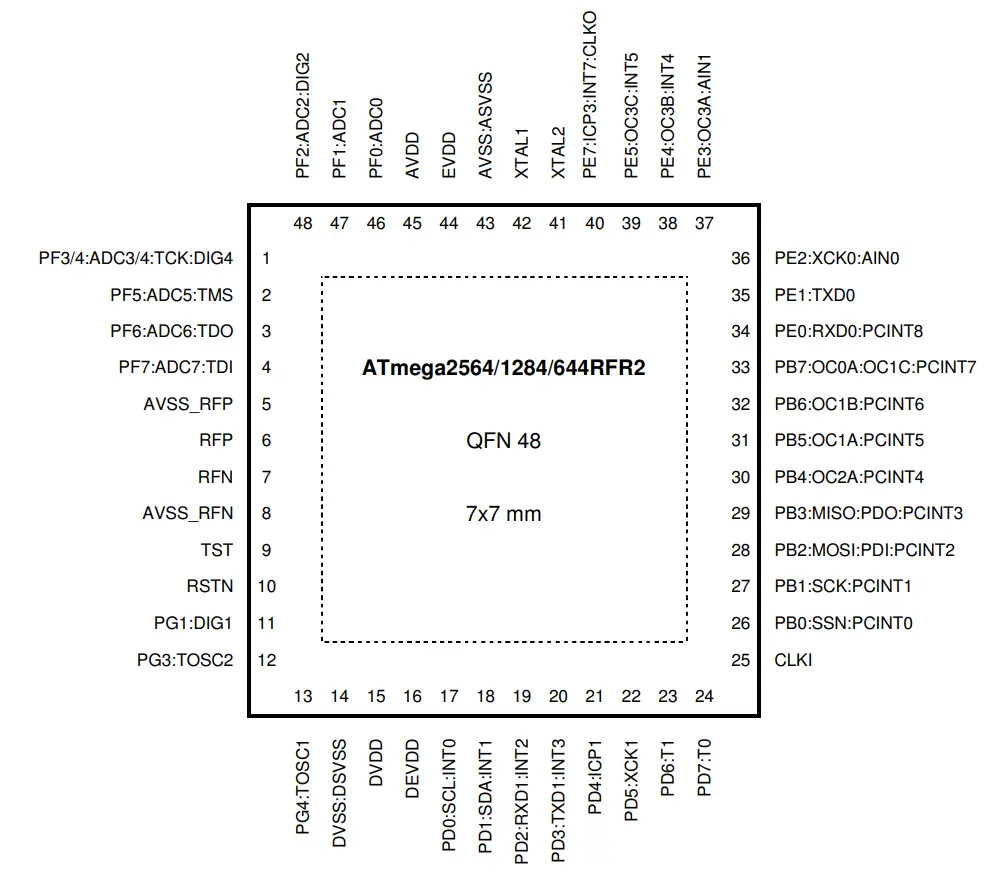

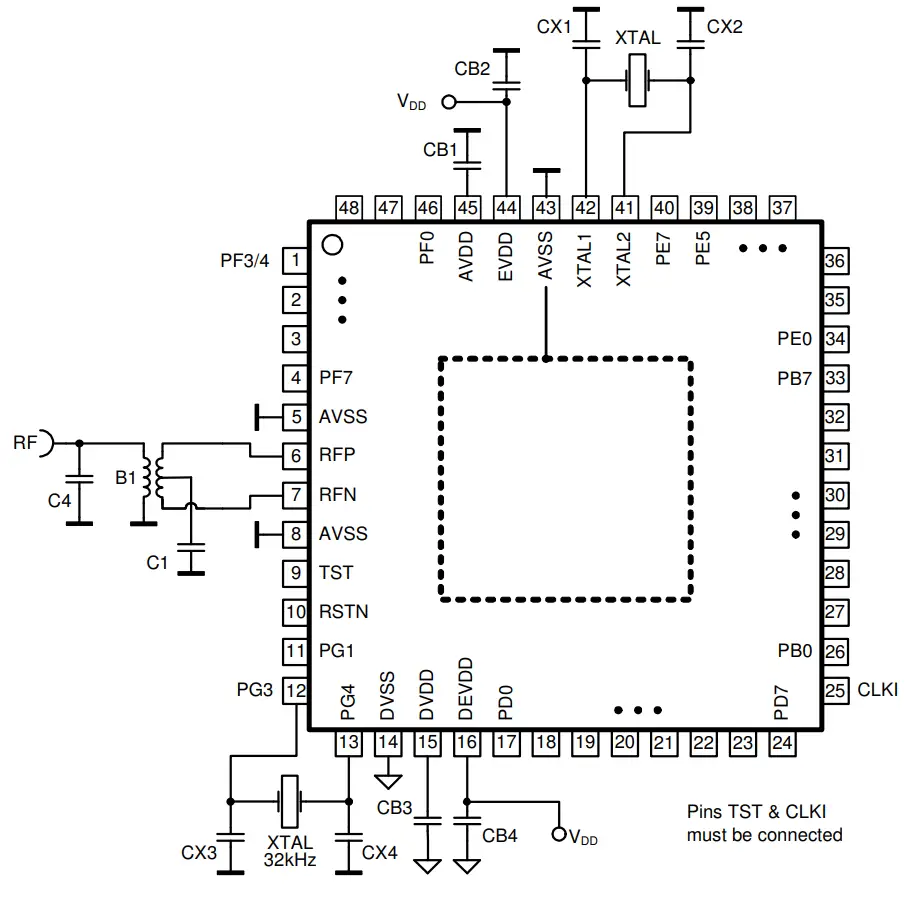

Cyfluniadau Pin

Ffigur 1-1. Pinout ATmega2564/1284/644RFR2

NodynMae'r pad canol mawr o dan y pecyn QFN/MLF wedi'i wneud o fetel ac wedi'i gysylltu'n fewnol ag AVSS. Dylid ei sodro neu ei ludo i'r bwrdd i sicrhau sefydlogrwydd mecanyddol da. Os na chaiff y pad canol ei gysylltu, gallai'r pecyn lacio o'r bwrdd. Ni argymhellir defnyddio'r padl agored yn lle'r pinnau AVSS rheolaidd.

Ymwadiad

Mae'r gwerthoedd nodweddiadol sydd wedi'u cynnwys yn y daflen ddata hon yn seiliedig ar ganlyniadau efelychu a nodweddu microreolyddion AVR eraill a thrawsyrwyr radio a weithgynhyrchwyd mewn technoleg proses debyg. Bydd gwerthoedd Isafswm ac Uchaf ar gael ar ôl i'r ddyfais gael ei nodweddu.

Drosoddview

Mae'r ATmega2564/1284/644RFR2 yn ficroreolydd CMOS 8-bit pŵer isel sy'n seiliedig ar bensaernïaeth RISC wedi'i gwella gan AVR ynghyd â thrawsyrgydd cyfradd data uchel ar gyfer y band ISM 2.4 GHz.

Drwy weithredu cyfarwyddiadau pwerus mewn un cylchred cloc, mae'r ddyfais yn cyflawni trwybynnau sy'n agosáu at 1 MIPS fesul MHz gan ganiatáu i ddylunydd y system optimeiddio'r defnydd o bŵer yn erbyn cyflymder prosesu.

Mae'r trawsderbynydd radio yn darparu cyfraddau data uchel o 250 kb/s hyd at 2 Mb/s, trin fframiau, sensitifrwydd derbynnydd rhagorol a phŵer allbwn trosglwyddo uchel sy'n galluogi cyfathrebu diwifr cadarn iawn.

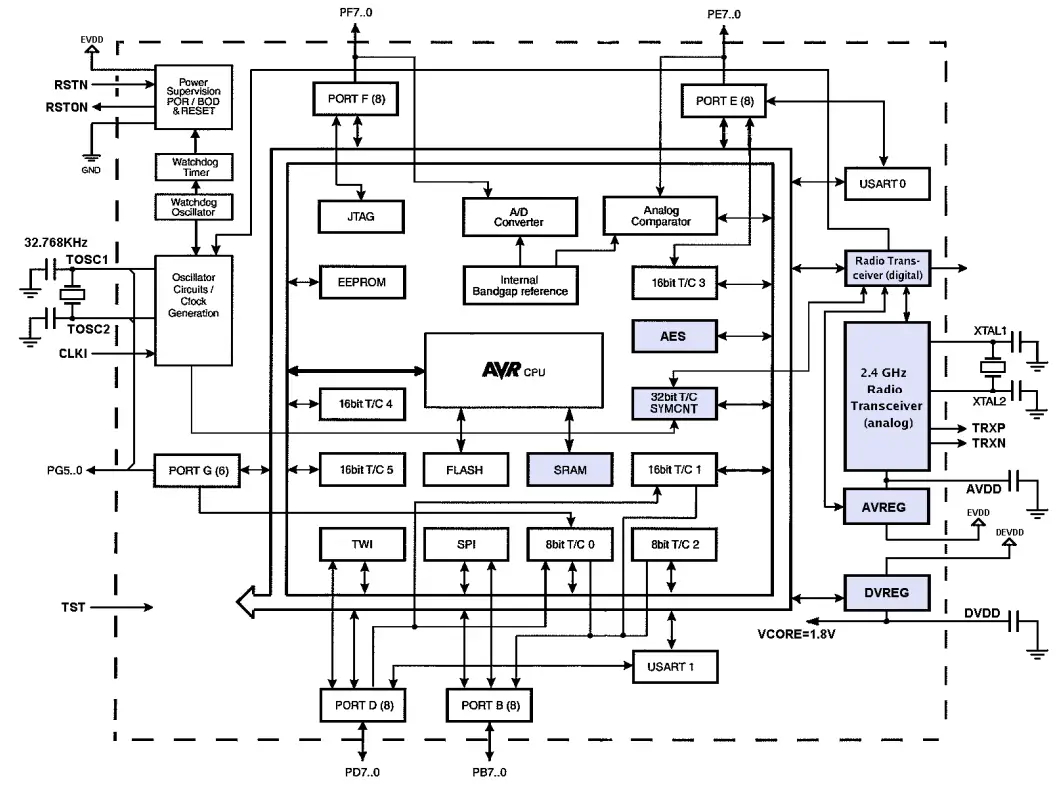

Diagram Bloc

Ffigur 3-1 Diagram Bloc

Mae craidd yr AVR yn cyfuno set gyfarwyddiadau gyfoethog â 32 o gofrestrau gweithio cyffredinol. Mae pob un o'r 32 o gofrestrau wedi'u cysylltu'n uniongyrchol â'r Uned Rhesymeg Rhifyddeg (ALU). Gellir cael mynediad at ddwy gofrestr annibynnol gydag un cyfarwyddyd sengl yn cael ei weithredu mewn un cylchred cloc. Mae'r bensaernïaeth sy'n deillio o hyn yn effeithlon iawn o ran cod wrth gyflawni trwybynnau hyd at ddeg gwaith yn gyflymach na microreolyddion CISC confensiynol. Mae'r system yn cynnwys cyfaint mewnol.tagrheoleiddio e a rheolaeth pŵer uwch. Wedi'i nodweddu gan y cerrynt gollyngiad bach mae'n caniatáu amser gweithredu estynedig o'r batri.

Mae'r trawsderbynydd radio yn ddatrysiad ZigBee cwbl integredig sy'n defnyddio nifer lleiaf o gydrannau allanol. Mae'n cyfuno perfformiad RF rhagorol â chost isel, maint bach a defnydd cerrynt isel. Mae'r trawsderbynydd radio yn cynnwys syntheseiddydd ffracsiynol-N wedi'i sefydlogi â grisial, trosglwyddydd a derbynnydd, a phrosesu Signal Sbectrwm Lledaenu Dilyniant Uniongyrchol (DSSS) llawn gyda lledaenu a dad-ledaenu. Mae'r ddyfais yn gwbl gydnaws â safonau IEEE802.15.4-2011/2006/2003 a ZigBee. Mae'r ATmega2564/1284/644RFR2 yn darparu'r nodweddion canlynol: 256K/128K/64K Beit o Fflach Rhaglenadwy Mewn-System (ISP) gyda galluoedd darllen-wrth-ysgrifennu, EEPROM 8K/4K/2K Beit, SRAM 32K/16K/8K Beit, hyd at 35 llinell Mewnbwn/Allbwn pwrpas cyffredinol, 32 cofrestr gweithio pwrpas cyffredinol, Cownter Amser Real (RTC), 6 Amserydd/Cownter hyblyg gyda moddau cymharu a PWM, Amserydd/Cownter 32 bit, 2 USART, Rhyngwyneb Cyfresol 2-wifren wedi'i gyfeirio at beit, trawsnewidydd analog i ddigidol (ADC) 8 sianel, 10 bit gyda mewnbwn gwahaniaethol dewisol.tage gydag enillion rhaglenadwy, Amserydd Gwarchod rhaglenadwy gydag Osgilydd Mewnol, porthladd cyfresol SPI, cydymffurfiaeth â safon IEEE 1149.1 JTAG rhyngwyneb prawf, a ddefnyddir hefyd ar gyfer cyrchu'r system Dadfygio Ar-sglodion a rhaglennu a 6 modd arbed pŵer y gellir eu dewis o feddalwedd.

Mae'r modd Segur yn atal y CPU tra'n caniatáu i'r SRAM, yr Amserydd/Cyfrifwyr, y porthladd SPI, a'r system ymyrraeth barhau i weithredu. Mae'r modd Pŵer-i-Ddwyn i Lawr yn arbed cynnwys y gofrestr ond yn rhewi'r Osgilydd, gan analluogi pob swyddogaeth sglodion arall tan yr ymyrraeth neu ailosodiad caledwedd nesaf. Yn y modd Arbed Pŵer, mae'r amserydd anghydamserol yn parhau i redeg, gan ganiatáu i'r defnyddiwr gynnal sylfaen amserydd tra bod gweddill y ddyfais yn cysgu. Mae'r modd Lleihau Sŵn ADC yn atal y CPU a phob modiwl Mewnbwn/Allbwn ac eithrio'r amserydd anghydamserol a'r ADC, i leihau sŵn newid yn ystod trawsnewidiadau ADC. Yn y modd Wrth Gefn, mae'r osgilydd RC yn rhedeg tra bod gweddill y ddyfais yn cysgu. Mae hyn yn caniatáu cychwyn cyflym iawn ynghyd â defnydd pŵer isel. Yn y modd Wrth Gefn Estynedig, mae'r prif osgilydd RC a'r amserydd anghydamserol yn parhau i redeg.

Dangosir cerrynt cyflenwi nodweddiadol y microreolydd gyda chloc y CPU wedi'i osod i 16MHz a'r trawsderbynydd radio ar gyfer y cyflyrau pwysicaf yn Ffigur 3-2 isod.

Ffigur 3-2 Cerrynt cyflenwi trawsyrrydd radio a microreolydd (16MHz)

Mae pŵer allbwn y trosglwyddo wedi'i osod i'r uchafswm. Os yw'r trawsderbynydd radio yn y modd CYSGU, dim ond y microreolydd AVR sy'n gwasgaru'r cerrynt.

Yn y modd Cwsg Dwfn, mae pob bloc digidol mawr heb unrhyw ofynion cadw data yn cael eu datgysylltu o'r prif gyflenwad gan ddarparu cerrynt gollyngiad bach iawn. Gellir ffurfweddu'r amserydd gwylio, y cownter symbol MAC a'r osgiliadur 32.768kHz i barhau i redeg.

Mae'r ddyfais wedi'i chynhyrchu gan ddefnyddio technoleg cof anweddol dwysedd uchel Atmel.

Mae'r Flash ISP ar y sglodion yn caniatáu i'r cof rhaglen gael ei ailraglennu yn y system trwy ryngwyneb cyfresol SPI, gan raglennydd cof anweddol confensiynol, neu gan raglen gychwyn ar y sglodion sy'n rhedeg ar graidd yr AVR. Gall y rhaglen gychwyn ddefnyddio unrhyw ryngwyneb i lawrlwytho'r rhaglen gymhwysiad yng nghof Flash y cymhwysiad.

Bydd meddalwedd yn yr adran Flash cychwyn yn parhau i redeg tra bod adran Flash y rhaglen yn cael ei diweddaru, gan ddarparu gweithrediad Darllen-Wrth-Ysgrifennu gwirioneddol. Drwy gyfuno CPU RISC 8 bit â Flash Hunan-Raglenadwy Mewn-System ar sglodion monolithig, mae'r Atmel ATmega2564/1284/644RFR2 yn ficroreolydd pwerus sy'n darparu ateb hynod hyblyg a chost-effeithiol i lawer o gymwysiadau rheoli mewnosodedig.

Mae'r ATmega2564/1284/644RFR2 AVR yn cael ei gefnogi gan gyfres lawn o offer datblygu rhaglenni a systemau gan gynnwys: crynhoydd C, cydosodwyr macro, dadfygiwr/efelychwyr rhaglenni, efelychwyr mewn-gylched, a phecynnau gwerthuso.

Disgrifiadau Pin

EVDD

Cyflenwad analog allanol cyftage.

DEVDD

Cyfrol cyflenwad digidol allanoltage.

AVDD

Cyfaint cyflenwad analog rheoleiddiedigtage (a gynhyrchwyd yn fewnol).

DVDD

Cyfrol cyflenwad digidol rheoleiddiedigtage (a gynhyrchwyd yn fewnol).

DVSS

Tir digidol.

AVSS

Tir analog.

Porthladd B (PB7…PB0)

Mae Porth B yn borthladd I/O deugyfeiriadol 8-did gyda gwrthyddion tynnu i fyny mewnol (a ddewisir ar gyfer pob did). Mae gan glustogau allbwn Porth B nodweddion gyriant cymesur gyda gallu sinc a ffynhonnell uchel. Fel mewnbynnau, bydd pinnau Port B sy'n cael eu tynnu'n allanol yn isel yn dod o hyd i gerrynt os caiff y gwrthyddion tynnu i fyny eu hactifadu. Mae'r pinnau Port B yn dri-nodi pan fydd cyflwr ailosod yn dod yn weithredol, hyd yn oed os nad yw'r cloc yn rhedeg.

Mae Porthladd B hefyd yn darparu swyddogaethau amrywiol nodweddion arbennig yr ATmega2564/1284/644RFR2.

Porthladd D (PD7…PD0)

Mae Porth D yn borthladd I/O deugyfeiriadol 8-did gyda gwrthyddion tynnu i fyny mewnol (a ddewisir ar gyfer pob did). Mae gan y byfferau allbwn Porth D nodweddion gyriant cymesur gyda gallu sinc a ffynhonnell uchel. Fel mewnbynnau, bydd pinnau Port D sy'n cael eu tynnu'n allanol yn isel yn dod o hyd i gerrynt os caiff y gwrthyddion tynnu i fyny eu hactifadu. Mae'r pinnau Port D yn dri-nodi pan fydd cyflwr ailosod yn dod yn weithredol, hyd yn oed os nad yw'r cloc yn rhedeg.

Mae Porth D hefyd yn darparu swyddogaethau amrywiol nodweddion arbennig yr ATmega2564/1284/644RFR2.

Porthladd E (PE7,PE5…PE0)

Yn fewnol, mae Porthladd E yn borthladd I/O deu-gyfeiriadol 8-bit gyda gwrthyddion tynnu i fyny mewnol (a ddewisir ar gyfer pob bit). Mae gan fwfferau allbwn Porthladd E nodweddion gyrru cymesur gyda gallu sinc a ffynhonnell uchel. Fel mewnbynnau, bydd pinnau Porthladd E sy'n cael eu tynnu'n isel yn allanol yn ffynhonnellu cerrynt os yw'r gwrthyddion tynnu i fyny yn cael eu actifadu. Mae pinnau Porthladd E wedi'u tri-gyfrif pan fydd cyflwr ailosod yn dod yn weithredol, hyd yn oed os nad yw'r cloc yn rhedeg.

Oherwydd nifer isel y pinnau yn y pecyn QFN48, nid yw porthladd E6 wedi'i gysylltu â phin. Mae porthladd E hefyd yn darparu swyddogaethau amrywiol nodweddion arbennig yr ATmega2564/1284/644RFR2.

Port F (PF7..PF5,PF4/3,PF2…PF0)

Yn fewnol, mae Porthladd F yn borthladd I/O deu-gyfeiriadol 8-bit gyda gwrthyddion tynnu i fyny mewnol (a ddewisir ar gyfer pob bit). Mae gan fwfferau allbwn Porthladd F nodweddion gyrru cymesur gyda gallu sinc a ffynhonnell uchel. Fel mewnbynnau, bydd pinnau Porthladd F sy'n cael eu tynnu'n isel yn allanol yn ffynhonnellu cerrynt os yw'r gwrthyddion tynnu i fyny yn cael eu actifadu. Mae pinnau Porthladd F wedi'u tri-gyfrif pan fydd cyflwr ailosod yn dod yn weithredol, hyd yn oed os nad yw'r cloc yn rhedeg.

Oherwydd nifer isel y pinnau yn y pecyn QFN48, mae porthladdoedd F3 ac F4 wedi'u cysylltu â'r un pin. Dylid gwneud y ffurfweddiad Mewnbwn/Allbwn yn ofalus er mwyn osgoi gormod o afradu pŵer.

Mae Porthladd F hefyd yn darparu swyddogaethau amrywiol nodweddion arbennig yr ATmega2564/1284/644RFR2.

Porthladd G (PG4, PG3, PG1)

Yn fewnol, mae Porthladd G yn borthladd I/O dwyffordd 6-bit gyda gwrthyddion tynnu i fyny mewnol (a ddewisir ar gyfer pob bit). Mae gan fwfferau allbwn Porthladd G nodweddion gyrru cymesur gyda gallu sinc a ffynhonnell uchel. Fodd bynnag, mae cryfder gyrrwr PG3 a PG4 wedi'i leihau o'i gymharu â'r pinnau porthladd eraill. Mae'r gyfaint allbwntagMae'r gostyngiad e (VOH, VOL) yn uwch tra bod y cerrynt gollyngiad yn llai. Fel mewnbynnau, bydd pinnau Porth G sy'n cael eu tynnu'n isel yn allanol yn cynhyrchu cerrynt os yw'r gwrthyddion tynnu i fyny yn cael eu actifadu. Mae'r pinnau Porth G wedi'u tri-gyfrif pan fydd cyflwr ailosod yn dod yn weithredol, hyd yn oed os nad yw'r cloc yn rhedeg.

Oherwydd nifer isel y pinnau yn y pecyn QFN48, nid yw porthladd G0, G2 a G5 wedi'u cysylltu â phin.

Mae Porth G hefyd yn darparu swyddogaethau amrywiol nodweddion arbennig yr ATmega2564/1284/644RFR2.

CAIS_AVSS

Mae AVSS_RFP yn bin daear pwrpasol ar gyfer y porthladd RF I/O gwahaniaethol, dwyffordd.

AVSS_RFN

Mae AVSS_RFN yn bin daear pwrpasol ar gyfer y porthladd RF I/O gwahaniaethol, dwyffordd.

RFP

RFP yw'r derfynell bositif ar gyfer y porthladd RF I/O gwahaniaethol, dwyffordd.

RFN

RFN yw'r derfynell negyddol ar gyfer y porthladd RF I/O gwahaniaethol, dwyffordd.

RSTN

Mewnbwn ailosod. Bydd lefel isel ar y pin hwn am gyfnod hirach na'r hyd pwls lleiaf yn cynhyrchu ailosodiad, hyd yn oed os nad yw'r cloc yn rhedeg. Nid oes sicrwydd y bydd pwls byrrach yn cynhyrchu ailosodiad.

XTAL1

Mewnbwn i'r osgiliadur crisial 16MHz gwrthdroadol amplifer. Yn gyffredinol, mae grisial rhwng XTAL1 ac XTAL2 yn darparu'r cloc cyfeirio 16MHz ar gyfer y trawsderbynydd radio.

XTAL2

Allbwn yr osgiliadur grisial 16MHz gwrthdroadol ampllewywr.

TST

Pin galluogi modd rhaglennu a phrofi. Os na ddefnyddir pin TST tynnwch ef i'r lefel isel.

CLKI

Mewnbwn i'r system cloc. Os caiff ei ddewis, mae'n darparu cloc gweithredu'r microreolydd.

Pinnau Heb eu Defnyddio

Gall pinnau arnofiol achosi afradu pŵer yn y mewnbynnau digidoltage. Dylent fod wedi'u cysylltu â ffynhonnell briodol. Mewn moddau gweithredu arferol gellir galluogi'r gwrthyddion tynnu i fyny mewnol (yn Ailosod mae pob GPIO wedi'i ffurfweddu fel mewnbwn ac nid yw'r gwrthyddion tynnu i fyny wedi'u galluogi o hyd).

Ni ddylid cysylltu pinnau I/O dwyffordd â'r ddaear na'r cyflenwad pŵer yn uniongyrchol.

Rhaid cysylltu'r pinnau mewnbwn digidol TST a CLKI. Os na ddefnyddir, gellir cysylltu pin TST ag AVSS tra bod angen cysylltu CLKI â DVSS.

Mae pinnau allbwn yn cael eu gyrru gan y ddyfais ac nid ydynt yn arnofio. Mae pinnau cyflenwad pŵer, priod binnau cyflenwad daear, wedi'u cysylltu â'i gilydd yn fewnol.

Ni fydd XTAL1 ac XTAL2 byth yn cael eu gorfodi i gyflenwi cyfainttage ar yr un pryd.

Cydnawsedd a Chyfyngiadau Nodweddion Pecyn QFN-48

AREF

Mae'r cyfeirnod cyftagNid yw allbwn y trawsnewidydd A/D wedi'i gysylltu â phin yn yr ATmega2564/1284/644RFR2.

Porthladd E6

Nid yw'r porthladd E6 wedi'i gysylltu â phin yn yr ATmega2564/1284/644RFR2. Nid yw'r pin arall yn gweithredu fel mewnbwn cloc i amserydd 3 ac nid yw ymyrraeth allanol 6 ar gael.

Porthladd F3 ac F4

Mae'r porthladd F3 ac F4 wedi'u cysylltu â'r un pin yn yr ATmega2564/1284/644RFR2. Dylid gwneud y ffurfweddiad allbwn yn ofalus er mwyn osgoi defnydd cerrynt gormodol.

Defnyddir swyddogaeth pin arall porthladd F4 gan y JTAG rhyngwyneb. Os bydd y JTAG Os defnyddir rhyngwyneb rhaid ffurfweddu'r porthladd F3 fel mewnbwn a rhaid analluogi'r allbwn swyddogaeth pin amgen DIG4 (dangosydd RX/TX). Fel arall, y JTAG Ni fydd y rhyngwyneb yn gweithio. Dylid rhaglennu'r Ffiws SPIEN er mwyn gallu dileu rhaglen sy'n gyrru porthladd F3 ar ddamwain.

Dim ond 7 sianel fewnbwn un pen sydd ar gael i'r ADC.

Porthladd G0

Nid yw'r porthladd G0 wedi'i gysylltu â phin yn yr ATmega2564/1284/644RFR2. Nid yw'r swyddogaeth pin amgen DIG3 (dangosydd RX/TX gwrthdro) ar gael. Os yw'r JTAG os na ddefnyddir y rhyngwyneb, gellir defnyddio allbwn swyddogaeth pin amgen DIG4 porthladd F3 fel dangosydd RX/TX o hyd.

Porthladd G2

Nid yw'r porthladd G2 wedi'i gysylltu â phin yn yr ATmega2564/1284/644RFR2. Nid yw'r swyddogaeth pin amgen AMR (mewnbwn darllen mesurydd awtomataidd anghydamserol i amserydd 2) ar gael.

Porthladd G5

Nid yw'r porthladd G5 wedi'i gysylltu â phin yn yr ATmega2564/1284/644RFR2. Nid yw'r swyddogaeth pin amgen OC0B (sianel gymharu allbwn yr amserydd 8-Did 0) ar gael.

RSTON

Nid yw allbwn ailosod RSTON sy'n signalu'r cyflwr ailosod mewnol wedi'i gysylltu â phin yn yr ATmega2564/1284/644RFR2.

Crynodeb ffurfweddu

Yn ôl gofynion y cymhwysiad, mae maint cof amrywiol yn caniatáu optimeiddio'r defnydd o gerrynt a'r cerrynt gollyngiad.

Tabl 3-1 Ffurfweddiad Cof

| Dyfais | Fflach | EEPROM | SRAM |

| ATmega2564RFR2 | 256KB | 8KB | 32KB |

| ATmega1284RFR2 | 128KB | 4KB | 16KB |

| ATmega644RFR2 | 64KB | 2KB | 8KB |

Mae'r pecyn a'r cyfluniad pin cysylltiedig yr un peth ar gyfer pob dyfais sy'n darparu swyddogaeth lawn i'r rhaglen.

Tabl 3-2 Ffurfweddiad System

| Dyfais | Pecyn | GPIO | Cyfresol IF | Sianel ADC |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

Mae'r dyfeisiau wedi'u optimeiddio ar gyfer cymwysiadau yn seiliedig ar y fanyleb ZigBee a IEEE 802.15.4. Dylai cael pentwr cymwysiadau, haen rhwydwaith, rhyngwyneb synhwyrydd a rheolaeth pŵer ragorol wedi'u cyfuno mewn un sglodion fod yn bosibl am flynyddoedd lawer o weithredu.

Tabl 3-3 Cymhwysiad Profile

| Dyfais | Cais |

| ATmega2564RFR2 | Cydlynydd Rhwydwaith Mawr / Llwybrydd ar gyfer IEEE 802.15.4 / ZigBee Pro |

| ATmega1284RFR2 | Cydlynydd Rhwydwaith / Llwybrydd ar gyfer IEEE 802.15.4 |

| ATmega644RFR2 | Dyfais nod terfynol / prosesydd rhwydwaith |

Cylchedau Cais

Cynllun Cymhwysiad Sylfaenol

Dangosir cynllun cymhwysiad sylfaenol o'r ATmega2564/1284/644RFR2 gyda chysylltydd RF un pen yn Ffigur 4-1 isod a'r Bil Deunydd cysylltiedig yn Nhabl 4-1 ar dudalen 10. Mae'r mewnbwn RF un pen 50Ω yn cael ei drawsnewid i'r impedans porthladd RF gwahaniaethol 100Ω gan ddefnyddio Balun B1. Mae'r cynwysyddion C1 a C2 yn darparu cyplu AC o'r mewnbwn RF i'r porthladd RF, mae cynhwysydd C4 yn gwella paru.

Ffigur 4-1. Cynllun Cymhwysiad Sylfaenol (pecyn 48-pin)

Mae cynwysyddion osgoi'r cyflenwad pŵer (CB2, CB4) wedi'u cysylltu â'r pin cyflenwad analog allanol (EVDD, pin 44) a'r pin cyflenwad digidol allanol (DEVDD, pin 16). Mae'r cynhwysydd C1 yn darparu'r cyplu AC gofynnol o RFN/RFP.

Gall pinnau arnofiol achosi gormod o afradu pŵer (e.e. wrth droi'r pŵer ymlaen). Dylid eu cysylltu â ffynhonnell briodol. Ni ddylid cysylltu GPIO â'r ddaear na'r cyflenwad pŵer yn uniongyrchol.

Rhaid cysylltu'r pinnau mewnbwn digidol TST a CLKI. Os na fydd pin TST byth yn cael ei ddefnyddio, gellir ei gysylltu ag AVSS tra gellir cysylltu pin CLKI nas defnyddir â DVSS (gweler y bennod “Pinnau Heb eu Defnyddio”).

Mae cynwysyddion CB1 a CB3 yn gynwysyddion osgoi ar gyfer y cyfaint analog a digidol integredig.tagrheoleiddwyr e i sicrhau gweithrediad sefydlog ac i wella imiwnedd sŵn.

Dylid gosod cynwysyddion mor agos â phosibl at y pinnau a dylent fod â chysylltiad gwrthiant isel ac anwythiant isel â'r ddaear i gyflawni'r perfformiad gorau.

Mae'r grisial (XTAL), y ddau gynhwysydd llwyth (CX1, CX2), a'r gylchedwaith mewnol sydd wedi'i gysylltu â phinnau XTAL1 ac XTAL2 yn ffurfio'r osgiliadur grisial 16MHz ar gyfer y trawsderbynydd 2.4GHz. Er mwyn cyflawni'r cywirdeb a'r sefydlogrwydd gorau o ran amledd cyfeirio, rhaid osgoi cynwyseddau parasitig mawr. Dylid llwybro llinellau crisial mor fyr â phosibl ac nid yn agos at signalau Mewnbwn/Allbwn digidol. Mae hyn yn arbennig o ofynnol ar gyfer y Moddau Cyfradd Data Uchel.

Mae'r grisial 32.768 kHz sydd wedi'i gysylltu â'r osgiliadur grisial pŵer isel mewnol (is 1µA) yn darparu cyfeirnod amser sefydlog ar gyfer pob modd pŵer isel gan gynnwys Cownter Symbol IEEE 802.15.4 32 Bit (“Cownter Symbol MAC”) a chymhwysiad cloc amser real gan ddefnyddio'r amserydd anghydamserol T/C2 (“Amserydd/Cownter2 gyda PWM ac Ymgyrch Anghydamserol”).

Ni ddylai cyfanswm y cynhwysedd shunt gan gynnwys CX3, CX4 fod yn fwy na 15pF ar draws y ddau bin.

Mae cerrynt cyflenwad isel iawn yr osgiliadur yn gofyn am gynllun gofalus o'r PCB a rhaid osgoi unrhyw lwybr gollyngiadau.

Gall croestalk a phelydriad o newid signalau digidol i'r pinnau crisial neu'r pinnau RF ddirywio perfformiad y system. Argymhellir rhaglennu gosodiadau cryfder gyrru lleiaf ar gyfer y signal allbwn digidol (gweler “DPDS0 – Cofrestr Cryfder Gyrrwr Porthladd 0”).

Tabl 4-1. Bil Deunyddiau (BoM)

| Dynodwr | Disgrifiad | Gwerth | Gwneuthurwr | Rhif Rhan | Sylw |

| B1 | Balwn SMD

Balwn / hidlydd SMD |

2.4 GHz | Technoleg Wuerth Johanson | 748421245

2450FB15L0001 |

Hidlydd wedi'i gynnwys |

| CB1 CB3 | LDO VREG

cynhwysydd osgoi |

1 mF (isafswm o 100nF) | AVX

Murata |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10% 16V |

| CB2 CB4 | Cynhwysydd osgoi cyflenwad pŵer | 1 mF (isafswm o 100nF) | |||

| CX1, CX2 | Cynhwysydd llwyth crisial 16MHz | 12 pF | AVX

Murata |

06035A120JA GRP1886C1H120JA01 | COG (0603) 5% 50V |

| CX3, CX4 | Cynhwysydd llwyth crisial 32.768kHz | 12 … 25 pF | |||

| C1, C2 | cynhwysydd cyplu RF | 22 pF | Epcos Epcos AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50V (0402 neu 0603) |

| C4 (dewisol) | Paru RF | 0.47 pF | Johnstech | ||

| XTAL | Grisial | CX-4025 16 MHz

SX-4025 16 MHz |

ACAL Taitjen Siward | XWBBPL-F-1 A207-011 | |

| XTAL 32kHz | Grisial | Rs=100 kOhm |

Hanes Adolygu

Sylwch fod rhifau'r tudalennau cyfeirio yn yr adran hon yn cyfeirio at y ddogfen hon. Mae'r diwygiad sy'n cyfeirio yn yr adran hon yn cyfeirio at yr adolygiad o'r ddogfen.

Diwyg. 42073BS-MCU Di-wifr-09/14

- Cynnwys heb ei newid – wedi'i ail-greu ar gyfer rhyddhau cyfunol gyda'r daflen ddata.

Diwyg. 8393AS-MCU Di-wifr-02/13

- Rhyddhad cychwynnol.

© 2014 Atmel Corporation. Cedwir pob hawl. / Diwyg.: 42073BS-MCU Wireless-09/14 Mae Atmel®, logo Atmel a chyfuniadau ohonynt, Enabling Unlimited Possibilities®, ac eraill yn nodau masnach cofrestredig neu'n nodau masnach Atmel Corporation neu ei his-gwmnïau. Gall termau ac enwau cynnyrch eraill fod yn nodau masnach eraill.

Ymwadiad: Darperir y wybodaeth yn y ddogfen hon mewn cysylltiad â chynhyrchion Atmel. Nid yw'r ddogfen hon, neu mewn cysylltiad â gwerthu cynhyrchion Atmel, yn rhoi unrhyw drwydded, yn benodol neu'n oblygedig, trwy estopel neu fel arall, i unrhyw hawl eiddo deallusol. AC EITHRIO FEL A NODIR YN Y TELERAU AC AMODAU GWERTHIANT ATMEL A LEOLIR AR YR ATMEL WEBSAFLE, NID YW ATMEL YN DYCHMYGU UNRHYW ATEBOLRWYDD O BLAID AC YN GWRTHOD UNRHYW WARANT MYNEGOL, GOBLYGEDIG NEU STATUDOL SY'N GYSYLLTIEDIG Â'I GYNHYRCHION GAN GYNNWYS, OND NID YN GYFYNGEDIG I'R GWARANT OBLYGEDIG O FYDDIN, CYFIAWNDER AR GYFER PERTHNASOL, ADDAS. NI FYDD ATMEL MEWN DIGWYDD YN ATEBOL AM UNRHYW DDIFROD UNIONGYRCHOL, ANUNIONGYRCHOL, GANLYNIADOL, COSBUS, ARBENNIG NEU ANGENRHEIDIOL (GAN GYNNWYS, HEB GYFYNGIAD, IAWNDAL COLLI AC ELW, Amhariad I FUSNES, NEU GOLLI GWYBODAETH SY'N CODI) Y DDOGFEN HON, HYD YN OED OS YW ATMEL WEDI EI HYSBYSIAD O BOSIBL DIFRODAU O'R FATH. Nid yw Atmel yn gwneud unrhyw sylwadau na gwarantau mewn perthynas â chywirdeb neu gyflawnrwydd cynnwys y ddogfen hon ac mae'n cadw'r hawl i wneud newidiadau i fanylebau a disgrifiadau cynhyrchion ar unrhyw adeg heb rybudd. Nid yw Atmel yn gwneud unrhyw ymrwymiad i ddiweddaru'r wybodaeth a gynhwysir yma. Oni bai y darperir yn benodol fel arall, nid yw cynhyrchion Atmel yn addas ar gyfer cymwysiadau modurol, ac ni chânt eu defnyddio mewn cymwysiadau modurol. Nid yw cynhyrchion Atmel wedi'u bwriadu, eu hawdurdodi na'u gwarantu i'w defnyddio fel cydrannau mewn cymwysiadau a fwriedir i gynnal neu gynnal bywyd.

Electroneg Llygoden

Dosbarthwr Awdurdodedig

Cliciwch i View Gwybodaeth am Brisiau, Rhestr, Cyflenwi a Chylch Bywyd:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

Cefnogaeth i Gwsmeriaid

Corfforaeth Atmel

1600 Gyriant Technoleg

San Jose, CA 95110

UDA

Ffôn: (+1)408-441-0311

Ffacs: (+1)408-487-2600

www.atmel.com

Dogfennau / Adnoddau

|

Atmel ATmega2564 8bit AVR Microcontroller [pdfLlawlyfr y Perchennog ATmega2564RFR2, ATmega1284RFR2, ATmega644RFR2, Microreolydd AVR 8bit ATmega2564, ATmega2564, Microreolydd AVR 8bit, Microreolydd AVR, Microreolydd |